Transceiver CW 20 m – Commutation Rx/Tx Switching

Festina lente, voil√† plusieurs semaines que je cogite cet article, √† lire, √† d√©cortiquer des sch√©mas. Apr√®s un temps de repos laissant se d√©canter les id√©es, j’entame ce sujet passionnant. Toute la difficult√© √† appr√©hender le dispositif de commutation vient de sa dispersion dans le sch√©ma √©lectronique. Dispersion inh√©rente aux fonctions √† commuter : RIT qui agit sur le VFO, MUTE qui agit sur l’amplification audio, QSK qui agit sur l’entr√©e du transceiver, interrupteur ON/OFF qui met sous tension l’√©metteur. Mon but consiste √† rassembler en un seul chapitre, √† synth√©tiser l’ensemble du dispositif.

1. Description générale

Comme le montre le sch√©ma fonctionnel, j’ai opt√© pour la commutation √©lectronique. Le manipulateur ou clef reste le seul √©l√©ment de commutation m√©canique utilis√© pour initier la commutation √©lectronique. La clef a 2 positions : OFF au repos et ON quand on appuie dessus. Ces 2 √©v√©nements d√©clencheurs ont pour effet de commuter les diff√©rentes fonctions du dispositif au moyen de transistors.

Pour m’appuyer sur une base solide, je suis parti de sch√©mas publi√©s par KD1JV. La figure 1 ci-dessous, montre le sch√©ma du dispositif de commutation.

Figure 1: Dispositif de commutation Rx/Tx

Figure 1: Dispositif de commutation Rx/Tx

![]() Télécharger les fichiers Kicad.

Télécharger les fichiers Kicad.

2. Modélisation de la clef

Fidèle à mon habitude, le dispositif sera passé au banc du simulateur LTspice.

Au début il y a une magnifique clef, peut être comme celle-ci, fabriquée par Jean-Claude F6FCO. Comment la modéliser sous LTspice ?

Un switch commandé par une tension.

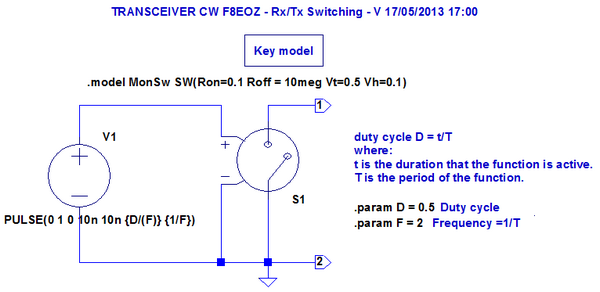

La figure 2 montre le circuit.

Figure 2: Circuit modèle de la clef

Figure 2: Circuit modèle de la clef

2.1. Subcircuit

Il est basé sur la NET LIST produite par LTspice. Pour créer un subcircuit on se reportera à cet article.

Paramètres du switch:

- Ron résistance du switch ON, très faible,

- Roff résistance du switch OFF, très élevée,

- e1 est le + de la tension de commande,

- e2 est le – de la tension de commande,

- Vt tension d¬īenclenchement de l¬īinterrupteur,

- Vh tension d¬īhyst√©r√©sis √† l¬īenclenchement, si V(e1, e2) < Vt – Vh/2 alors l¬īinterrupteur est ouvert, si V(e1, e2) > Vt + Vh/2 alors l¬īinterrupteur est ferm√©.

Paramètres du circuit:

- duty cycle D = t/T = 0,5,

- fréquence F = 2.

Avec ces valeurs, le switch sera ON et OFF 2 fois par seconde. La durée du ON = durée du OFF.

* C:\Users\Bernard\Documents\TCW20\tcw20RxTxSwitch\ltc\key.asc

* KEY - F8EOZ - V 17/05/2013 17:00

* KEY SUBCIRCUIT

* CONNECTIONS: 1

* | 2

* | |

.SUBCKT KEY 1 2 PARAMS: D=0.5s F=2

*--------------------------

* Key parameters:

* D = duty cycle = t/T

* where:

* t is the duration that the function is active

* T is the period of the function.

* F = frequency = 1/T

*--------------------------

V1 N001 0 PULSE(1 0 0 10n 10n {D/(F)} {1/F})

S1 0 1 N001 0 MonSW

.model MonSw SW(Ron=0.1 Roff = 10meg Vt=0.5 Vh=0.1)

.ENDS

Symbole

La cr√©ation d’un symbole est expliqu√©e dans cet article. La d√©finition des attributs est diff√©rente. Les param√®tres du mod√®le pourront √™tre modifi√©s au moment de son utilisation dans le mod√®le, par un simple clic droit sur le symbole. Ceci permet d’utiliser un seul symbole pour des ON/OFF diff√©rents. La figure 3 ci-dessous montre exactement comment la fen√™tre des attributs doit √™tre remplie pour un fonctionnement correct. La ligne SpiceLine contient les param√®tres par d√©faut de la cl√©: D=0.5s F=2 qui pourront √™tre modifi√©s lors de l’utilisation du symbole.

Dans le répertoire ../LTSPICEIV/lib/sym créer le répertoire key qui recevra vos symboles. Enregistrer le symbole key.asy dans ce répertoire.

Le symbole sera relié au subcircuit dans le modèle de simulation par la directive .lib key.sub

Figure 3: attributs du symbole key

Figure 3: attributs du symbole key

La figure 4 ci-dessous montre le dessin du symbole. Ces fichiers sont disponibles en téléchargement.

Figure 4: dessin du symbole key

Figure 4: dessin du symbole key

![]() Télécharger les fichiers LTspice.

Télécharger les fichiers LTspice.

3. Bloc Key Switch

3.1. Description

La clef commute un transistor PNP 2N3906. Quand la clef est OFF, le transistor au cutoff ne conduit pas. Quand la clef est ON, le transistor satur√© conduit. On se reportera √† l’article sur le trac√© de la caract√©ristique de transfert en tension qu’il est possible d’obtenir en utilisant LTspice. En sortie 2 lignes, TxVcc qui alimente les premiers √©tages de l’√©metteur et commande le bloc QSK Switch, TxLine qui commande les blocs suivants. La r√©sistance fictive Rload simule la charge repr√©sent√©e par les premiers √©tages de l’√©metteur.

3.2. Analyse en régime continu

Le schéma figure 5 ci-dessous, montre le circuit de simulation LTspice.

Figure 5: Bloc Key Switch РSimulation LTspice en régime continu

Figure 5: Bloc Key Switch РSimulation LTspice en régime continu

Ci-dessous les valeurs des tensions et courants obtenues quand la clef est ON:

V(c1): 13.8 voltage V(txvcc): 13.7459 voltage V(txline): 13.3544 voltage V(key): 0.000586371 voltage V(b1): 12.9007 voltage Ic(Q1): -0.0624945 device_current Ib(Q1): -0.00585471 device_current Ie(Q1): 0.0683492 device_current I(D1): 1.33544e-005 device_current I(R3): 1.33544e-005 device_current I(R2): 8.99258e-006 device_current I(Rload): 0.0624812 device_current I(R1): -0.00586371 device_current I(V1): -0.0683582 device_current Ix(u1:1): 0.00586371 subckt_current

![]() Télécharger les fichiers de simulation LTspice.

Télécharger les fichiers de simulation LTspice.

3.3. Analyse en régime variable

Le schéma figure 6 ci-dessous, montre le circuit de simulation LTspice.

Figure 6: Bloc Key Switch РSimulation LTspice en régime variable

Figure 6: Bloc Key Switch РSimulation LTspice en régime variable

La figure 7 ci-dessous, montre le graphe des tensions obtenu avec la clef réglée avec ses valeurs par défaut indiquées au paragraphe 2. La cellule R2C2 retarde la montée et la descente de la tension de la base du transistor Q1, retardant la commutation pour atténuer les key clicks. La diode D1 et la cellule R3C3 retardent la coupure de la tension de TxLine.

Figure 7: Bloc Key Switch – Graphe des tensions

Figure 7: Bloc Key Switch – Graphe des tensions

![]() Télécharger les fichiers de simulation LTspice.

Télécharger les fichiers de simulation LTspice.

4. Bloc QSK Switch

QSK – “Je peux vous entendre au cours de ma transmission” – parfois appel√© full break-in, d√©signe un mode de fonctionnement particulier du code Morse dans lequel le r√©cepteur est activ√© rapidement pendant les espaces entre les points et les traits, ce qui permet √† un autre op√©rateur d’ interrompre la transmission.

4.1. Description

L’antenne est connect√©e √† la sortie de l’√©metteur et √† l’entr√©e du r√©cepteur. En √©mission, le r√©cepteur doit √™tre isol√© de l’antenne. Trois transistors MOSFET canal N 2N7000 s’occupent de cette fonction. M2 relie le r√©cepteur √† l’antenne en r√©ception ou l’isole de l’antenne en √©mission. En raison des courants de fuite de M2, le r√©cepteur n’est pas compl√®tement isol√© du signal d’√©mission, M3 shunte l’entr√©e du r√©cepteur en √©mission. La tension de commande TxLine est appliqu√©e √† la grille de M3 et √† la grille de M1 qui commande M2. Quand la cl√© est appuy√©e pour √©mettre, alors M2 = OFF et M3 = ON. Quand la cl√© est rel√Ęch√©e pour recevoir, alors M2 = ON et M3 = OFF.

4.2. Analyse en régime continu

Le schéma figure 8 ci-dessous, montre le circuit de simulation LTspice.

Figure 8: Bloc QSK Switch РSimulation LTspice en régime continu

Figure 8: Bloc QSK Switch РSimulation LTspice en régime continu

Ci-dessous les valeurs des tensions et courants obtenues quand la clef est ON:

V(mute): 0.000263519 voltage V(txline): 13.3157 voltage V(txvcc): 13.7089 voltage V(key): 0.000585177 voltage V(b1): 12.8745 voltage V(rxin): 0 voltage V(ant): 0 voltage Ic(Q1): -0.137103 device_current Ib(Q1): -0.00584252 device_current Ie(Q1): 0.142945 device_current I(D1): 1.33157e-005 device_current Id(M3): 0 device_current Ig(M3): 0 device_current Ib(M3): 0 device_current Is(M3): 0 device_current Id(M2): 0 device_current Ig(M2): 0 device_current Ib(M2): 0 device_current Is(M2): 0 device_current Id(M1): 0.000137997 device_current Ig(M1): 0 device_current Ib(M1): -2.63934e-016 device_current Is(M1): -0.000137997 device_current I(Rload2): 0 device_current I(R3): 1.33157e-005 device_current I(R1): 9.25515e-006 device_current I(Rload): 0.137089 device_current I(R2): -0.00585177 device_current I(R4): 0.000137997 device_current I(V2): 0 device_current I(V1): -0.143092 device_current Ix(u1:1): 0.00585177 subckt_current

![]() Télécharger les fichiers LTspice.

Télécharger les fichiers LTspice.

4.3. Analyse en régime variable

Le sch√©ma figure 9 ci-dessous, montre le circuit de simulation LTspice. Avec cette simulation, j’ai atteint la limite des capacit√©s de calcul et d’affichage de mon ordinateur. J’ai d√Ľ en cons√©quence, limiter la fr√©quence du g√©n√©rateur d’entr√©e de l’antenne V2 √† 1 MHz et faire preuve de patiente, la simulation dure environ 35 mn.

Figure 9: Bloc QSK Switch РSimulation LTspice en régime variable

Figure 9: Bloc QSK Switch РSimulation LTspice en régime variable

La figure 10 ci-dessous, montre le graphe des tensions obtenu avec la clef r√©gl√©e avec ses valeurs par d√©faut indiqu√©es au paragraphe 2. La tension sinuso√Įdale (V2, F) = (1 V, 1 MHz) est inject√©e en permanence √† l’entr√©e de l’antenne. Le graphe du haut Vrxin montre que le signal entre dans le r√©cepteur √† partir de l’instant o√Ļ TxLine passe sous la tension de pincement. Ceci correspond aux espaces de temps pendant lesquels il est possible d’entendre un correspondant.

Au même moment Vmute = 13 V = NO_MUTE pendant 50 ms.

Figure 10: Bloc QSK Switch – Graphe des tensions

Figure 10: Bloc QSK Switch – Graphe des tensions

![]() Télécharger les fichiers LTspice.

Télécharger les fichiers LTspice.

5. Bloc RIT

Le “Receiver Incremental Tuning” ou RIT est la capacit√© de d√©caler l√©g√®rement la fr√©quence de r√©ception d’un √©metteur-r√©cepteur. Utilis√© soit d√©lib√©r√©ment pour avoir une fr√©quence d’√©mission diff√©rente de la fr√©quence de r√©ception et √™tre mieux entendu, soit pour compenser un d√©calage de fr√©quence.

5.1. Description

Une diode zener 1N4756 est ajout√©e en parall√®le sur le circuit d’accord du VFO. Le potentiom√®tre RV1 permet de faire varier sa capacit√© en r√©ception.

5.2. Analyse en régime continu

Le schéma figure 11 ci-dessous, montre le circuit de simulation LTspice. Pour simplifier, le circuit simule uniquement la variation de tension. Le potentiomètre est représenté par 2 résistances égales RV1 et RV2.

Figure 11: Bloc RIT РSimulation LTspice en régime continu

Figure 11: Bloc RIT РSimulation LTspice en régime continu

Ci-dessous les valeurs des tensions et courants obtenues quand la clef est ON:

V(c1): 13.8 voltage V(txvcc): 13.7089 voltage V(txline): 13.3157 voltage V(key): 0.000585177 voltage V(b1): 12.8745 voltage V(vrita): 3.00356 voltage V(vritb): 2.99644 voltage V(vcc6): 6 voltage V(n001): 3 voltage V(vrit): 3 voltage Ic(Q1): -0.137103 device_current Ib(Q1): -0.00584252 device_current Ie(Q1): 0.142945 device_current I(C5): 3e-019 device_current I(C3): 1.33157e-018 device_current I(C2): 4.24858e-017 device_current I(C1): -5.85177e-023 device_current I(D1): 1.33157e-005 device_current Id(M4): 0.00299637 device_current Ig(M4): 0 device_current Ib(M4): 4.44089e-013 device_current Is(M4): -0.00299637 device_current I(R7): 0 device_current I(Rv2): 7.12499e-008 device_current I(Rv1): 7.12499e-008 device_current I(R6): 0.00299644 device_current I(R5): 0.00299644 device_current I(R3): 1.33157e-005 device_current I(R1): 9.25515e-006 device_current I(Rload): 0.137089 device_current I(R2): -0.00585177 device_current I(V2): -0.00299644 device_current I(V1): -0.142954 device_current Ix(u1:1): 0.00585177 subckt_current

![]() Télécharger les fichiers de simulation LTspice.

Télécharger les fichiers de simulation LTspice.

5.3. Analyse en régime variable

Le schéma figure 12 ci-dessous, montre le circuit de simulation LTspice.

Figure 12: Bloc RIT РSimulation LTspice en régime variable

Figure 12: Bloc RIT РSimulation LTspice en régime variable

La figure 13 ci-dessous, montre le graphe des tensions obtenu avec la clef réglée avec ses valeurs par défaut indiquées au paragraphe 2. La tension inverse de diode peut être réglée entre Vritb = 0 V et Vrita = 6 V en réception. Elle reste fixée au repos, en émission, à 3 V. Dans ce cas M4 est ON, Vrita = Vrib = Vcc 6V/2 puisque R5 = R6.

Figure 13: Bloc RIT – Graphe des tensions

Figure 13: Bloc RIT – Graphe des tensions

![]() Télécharger les fichiers LTspice.

Télécharger les fichiers LTspice.

6. Bloc MUTE

Ce module rend muet le r√©cepteur, mais pas trop! Pendant l’√©mission il laisse passer faiblement le signal pour avoir une √©coute locale ou sidetone.

6.1. Description

Un transistor JFET Canal N 2N3819 commandé par la tension MUTE, fait ce travail. Au repos, clef OFF, la tension de grille = 13 V = NO_MUTE, le transistor conduit. En transmission, clef ON, la tension de grille = 0 V = MUTE, le transistor ne conduit pas, le signal est shunté par la résistance R7 qui laisse passer un signal faible.

6.2. Analyse en régime continu

Le sch√©ma figure 14 ci-dessous, montre le circuit de simulation LTspice. Pour simplifier et avoir une meilleure lisibilit√©, le signal MUTE est produit par le g√©n√©rateur d’impulsions V3. A la lumi√®re de la simulation du QSK Switch le Duty Cycle est r√©gl√© √† 50 ms/500 ms = 0,1.

Figure 14: Bloc Mute РSimulation LTspice en régime continu

Figure 14: Bloc Mute РSimulation LTspice en régime continu

Ci-dessous les valeurs des tensions et courants obtenues en réception quand la clef est OFF:

V(vcc): 13.8 voltage V(j1g): 13.2447 voltage V(no_mute): 13 voltage V(j1d): 13.8 voltage V(j1s): 13.8 voltage V(audio_amp): 1.38e-014 voltage V(proddet): 0 voltage I(C7): 1.38e-018 device_current I(C6): -1.32447e-019 device_current I(C5): 1.38e-018 device_current I(D2): 5.55306e-007 device_current Id(J1): 1.93421e-012 device_current Ig(J1): -1.93467e-012 device_current Is(J1): 4.66634e-016 device_current I(R8): -1.38e-018 device_current I(R7): 1.5358e-016 device_current I(R6): -5.55304e-007 device_current I(R5): 1.93506e-012 device_current I(V3): 5.55306e-007 device_current I(V2): 1.38e-018 device_current I(V1): -5.55306e-007 device_current

![]() Télécharger les fichiers de simulation LTspice.

Télécharger les fichiers de simulation LTspice.

6.3. Analyse en régime variable

Le schéma figure 15 ci-dessous, montre le circuit de simulation LTspice

Figure 15: Bloc MUTE РSimulation LTspice en régime variable

Figure 15: Bloc MUTE РSimulation LTspice en régime variable

La figure 16 ci-dessous, montre le graphe des tensions. La valeur du condensateur C6 initialement prévue à 100 nF a été ramenée à 10 nF. En effet, avec 100 nF le temps de montée de la tension de grille était trop long pour obtenir un fonctionnement correct.

Figure 16: Bloc MUTE – Graphe des tensions

Figure 16: Bloc MUTE – Graphe des tensions

![]() Télécharger les fichiers LTspice.

Télécharger les fichiers LTspice.

7. Réalisation РTests

Après une pause de plusieurs mois contrainte par un problème de santé, je reprends la plume et le fer à souder.

Je simplifie le probl√®me en le divisant en plusieurs √©tapes. D’abord, je v√©rifie le bon fonctionnement du r√©cepteur seul en d√©connectant l’√©metteur, ensuite le fonctionnement de l’√©metteur.

7.1. Bloc Key Switch et QSK Switch

Pour des raisons pratiques, j’ai r√©alis√© en m√™me temps ces 2 blocs.

7.1.1. Circuit imprimé

Suivant la m√©thode modulaire, chaque bloc est c√Ębl√© s√©par√©ment sur 2 plaques identiques. La photo 1 ci-dessous, montre les circuits r√©alis√©s sur 2 plaques d‚Äô√©poxy cuivr√©es simple face de 32 x 24 mm selon le mode de fabrication d√©crit dans les articles pr√©c√©dents. Le circuit trac√© est un quadrillage: 2 lignes de 8 mm + 2 lignes de 4 mm, 4 colonnes de 8 mm. Nous obtenons ainsi 2√ó4 = 8 √ģlots de 8√ó8 mm. Les 2 lignes de 4 mm, plac√©es de part et d‚Äôautre, servent de rail de masse soud√©s √† la carte m√®re. Les 2 blocs sont dispos√©s c√īte √† c√īte pr√®s de l’entr√©e du r√©cepteur. La ligne TxVcc et la ligne Mute ne sont pas encore connect√©es.

Photo 1: Circuit imprimé des blocs Key Switch et QSK Switch

Photo 1: Circuit imprimé des blocs Key Switch et QSK Switch

7.1.2. Test

Le test que je me propose de faire ici est simple:

- s’assurer que le r√©cepteur fonctionne correctement apr√®s l’insertion dans le circuit des blocs Key Switch et QSK Switch.

- s’assurer que le r√©cepteur est isol√© de l’antenne en mode √©mission.

Pour ce faire:

- toute la cha√ģne d’√©mission est mise hors tension: oscillateur, m√©langeur, pr√©-driver, driver,

- l’antenne est connect√©e √† fiche BNC,

- le r√©cepteur est cal√© sur une station en train d’√©mettre.

Je v√©rifie que le r√©cepteur fonctionne comme avant l’insertion des 2 blocs. Un simple bout de fil volant simule la cl√© et sert √† mettre ou non l’entr√©e Key In √† la masse (voir photo 1 ci-dessus). Je v√©rifie que la r√©ception est coup√©e ou non.

7.2. Bloc Mute

7.2.1. Circuit imprimé

Cette fois j’ai un peu modifi√© ma m√©thode de fabrication. A l’exception du transistor tous les composants sont des CMS ou SMD 1206 ou 0805. J’obtiens un circuit plus compact et plus clair. Le circuit est toujours compos√© d’√ģlots identiques juxtapos√©s. La taille des √ģlots a √©t√© r√©duite √† 6×6 mm. Un ou plusieurs √ģlots pouvant √™tre r√©unis pour n’en former qu’un seul. Seul les √ģlots utiles sont grav√©s ce qui rend un peu plus compliqu√©e la gravure. Un espace de 4mm environ est r√©serv√© pour la masse tout autour du circuit. Mieux qu’un long discours, la photo 2 ci-dessous, montre le circuit r√©alis√© sur 1 plaques d‚Äô√©poxy cuivr√©e simple face de 32 x 24 mm. Cette plaque a √©t√© enduite totalement au feutre noir non effa√ßable. Le circuit a √©t√© grav√© avec une pointe √† tracer puis plong√© dans un d√© √† coudre de perchlorure de fer. Le circuit est ensuite √©tam√© √† chaud. Nous obtenons ainsi un trac√© fin qui permet de souder sans probl√®me les minuscules composants. Les 2 lignes de 4 mm, plac√©es de part et d‚Äôautre, servent de rail de masse soud√©s √† la carte m√®re. La ligne NO_MUTE n’est pas encore connect√©e.

Photo 2: Circuit imprimé du bloc Mute

Photo 2: Circuit imprimé du bloc Mute

7.2.2. Test

Le test que je me propose de faire consiste à:

- s’assurer que le r√©cepteur fonctionne correctement sans Mute,

- s’assurer que le signal audio du r√©cepteur est tr√®s faible en position Mute.

Pour ce faire:

- le bloc QSK est déconnecté,

- l’antenne est connect√©e √† fiche BNC, reli√© directement au filtre passe-bande sans passer par le bloc QSK qui est shunt√©,

- Une charge fictive de 50 ő© est reli√©e √† la sortie du driver du PA qui n’est pas reli√© √† l’antenne pour ne pas polluer l’√©ther,

- la ligne NO_MUTE n’est pas connect√©e (en l’air),

- le bloc Mute est connecté à la carte mère, masse et Vcc,

- le r√©cepteur est cal√© sur une station en train d’√©mettre.

Surprise! Ce petit circuit m’a donn√© beaucoup de fil √† retordre. Seul un bourdonnement vibrait dans le casque. Je changeais tous les composants du circuit et rempla√ßais le 2N3819 par un MPF102. Miracle! Le r√©cepteur fonctionne. Etait-ce un composant d√©fectueux ? Je ne sais pas. Un petit bout de fil √† la main je connecte l’entr√©e NO_MUTE – active au niveau bas – du circuit √† la masse, je constate que la r√©ception est fortement affaiblie. Le circuit fait bien son travail! Au passage je suis √©tonn√© de la qualit√© de ce premier petit r√©cepteur. Les essais ont √©t√© r√©alis√©s le samedi 19 octobre 2013 entre 19h00 et 20h45 heure locale entre 14 et 14, 050 Mhz. Une foule de stations arrive dans les √©couteurs : Allemagne, Lithuanie, Bulgarie, Russie et √† mon grand √©tonnement je capte un CQ de K2NV du NYQP New York State QSO Party sur 14,047456Mhz. Mon antenne est un dip√īle taill√©e pour le 20m mais pour l’instant plac√©e provisoirement √† l’√©tage du QTH, les 2 branches du dip√īle se frayant un passage l√† o√Ļ elles peuvent!

7.3. Bloc RIT

7.3.1. Circuit imprimé

M√©thode identique au bloc Mute. Cette fois pour √©tamer le circuit, j’ai utilis√© la p√Ęte √† √©tamer Castotin sp 5423 achet√© dans un magasin de bricolage. La p√Ęte est √©tal√©e √† l’aide d’un pinceau sur le circuit. Inutile d’en mettre beaucoup. Elle est chauff√©e avec un d√©capeur thermique. Ne pas chauffer trop longtemps. D√®s que le circuit est couvert, arr√™ter. La photo 3 ci-dessous, montre le circuit r√©alis√© sur 1 plaque d‚Äô√©poxy cuivr√©e simple face de 32 x 26 mm. On remarque que la finesse du trac√© permet de souder les minuscules composants CMS 0805 entre chaque √ģlot. Le bloc est plac√© √† c√īt√© du VFO. La ligne Vcc 6V est reli√©e au VFO et la ligne TxLine au bloc Key Switch.

Photo 3: Circuit imprimé du bloc RIT

Photo 3: Circuit imprimé du bloc RIT

7.2.2. Test

Le test que je me propose de faire consiste observer le d√©calage de fr√©quence sur l’afficheur du fr√©quencem√®tre quand on manipule la cl√©.

Pour ce faire tous les blocs de commutation sont connectés:

- le bloc QSK est connecté,

- l’antenne est connect√©e √† fiche BNC,

- Une charge fictive de 50 ő© est reli√©e √† la sortie du driver du PA qui n’est pas reli√© √† l’antenne pour ne pas polluer l’√©ther,

- la ligne NO_MUTE est connectée,

- le bloc Mute est connecté à la carte mère, masse et Vcc,

- le récepteur est calé sur une fréquence dans la bande 20m.

Un petit bout de fil √† la main je connecte l’entr√©e Key du bloc Key Switch √† la masse. Je constate en r√©ception que la fr√©quence est d√©cal√©e et que le potentiom√®tre permet de r√©gler le d√©calage.

Références

The ADC-40 All Discrete Component transceiver Revised 6-23-09 – Steven WEBER KD1JV

The NADC A CW rig using Nearly All Discrete Components – Steven WEBER KD1JV

What_Causes_Clicks? by Tom Rauch W8JI

N5ESE’s Outboard T/R Switch

Index des articles de la catégorie Transceiver

- Transceiver CW 20 m

- Transceiver CW 20 m – Amplificateur audio

- Transceiver CW 20 m – Amplificateur IF CASCODE

- Transceiver CW 20 m РAmplificateur post-mélangeur

- Transceiver CW 20 m РAtténuateur en pi

- Transceiver CW 20 m – BFO

- Transceiver CW 20 m – Commutation Rx/Tx Switching

- Transceiver CW 20 m РDétecteur de produit

- Transceiver CW 20 m – Emetteur

- Transceiver CW 20 m – Filtre √† quartz ‚Äď Crystal ladder filter

- Transceiver CW 20 m – Filtre de sortie du PA

- Transceiver CW 20 m – M√©langeur ‚Äď Double Balanced Mixer

- Transceiver CW 20 m – Oscillateur et M√©langeur de l’√©metteur

- Transceiver CW 20 m – PA Driver

- Transceiver CW 20 m РRécepteur РAmplificateur RF

- Transceiver CW 20 m РRécepteur РFiltre passe bande 14 MHz

- Transceiver CW 20 m – VFO – Partie 1

- Transceiver CW 20 m – VFO – Partie 2

- Transceiver CW 20 m – VFO – Partie 3

- Transceiver CW 20 m – VFO – Partie 4

- Transceiver CW 20 m – VFO Version 2 ‚Äď Etalement de la bande